DDRx Simulation

Simulation Difficulties

- Large routing density, large number of particles, high operation speed, small timing margin, and many types of drives

Simulation Purpose

- Guide Layout

- If problems occur during project commissioning, locate the problems through simulation and put forward improvement suggestions

- If the signal inside the chip cannot be detected, the real situation inside the chip can be simulated by comparing the external test data through simulation

Simulation Content

- Topology optimization, ODT regulation, drive selection, termination/series resistance regulation, timing analysis, full-channel simulation for all signal lines

Simulation Significance

- Guide Layout

- (LP)DDR3/4/5、GDDR6 topology type selection

- When low power consumption is required, can the ODT be turned off and work normally

- (LP)DDR3/4/5、GDDR6 design guidance for high-density and cost-reduction (such as layer reduction and common process)

- There is no complete reference plane in HDI design or the wiring guidance cannot be very good when the length is equal

Simulation object

DDR (LPDDR) 3/4/5 full channel simulation

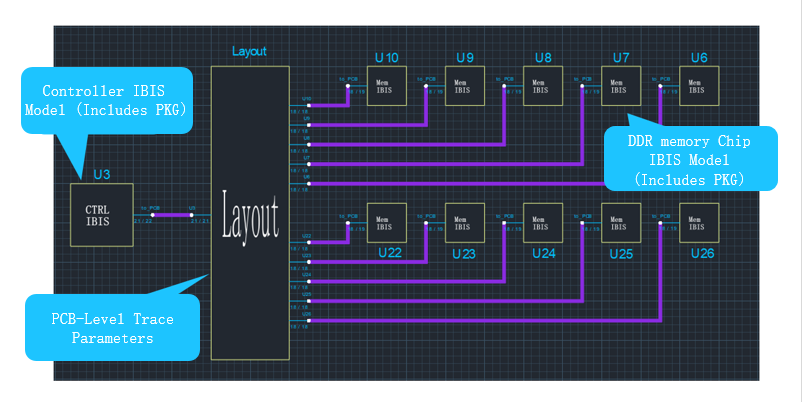

A Domestic CPU Chip DDR5-1-to-10 Topology On-Board Memory Full-Channel Simulation Case

Simulation Case of a Domestic CPU with DDR5 Full-Channel

Design experience

EDADOC Technology's design experience of more than 15000 models per year has created the industry's leading DDR simulation technology

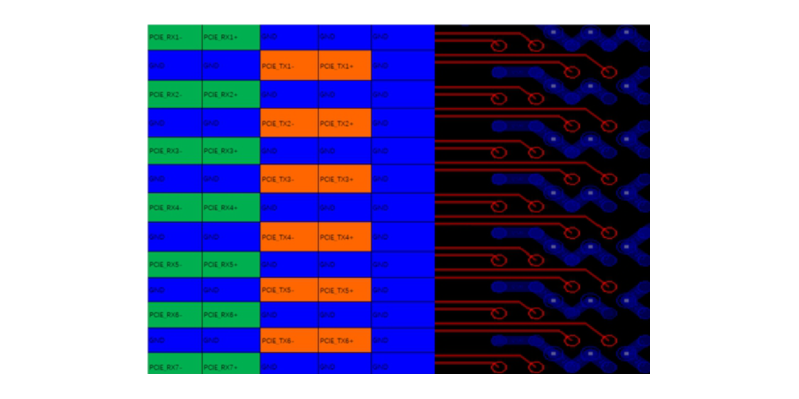

The following figure shows the popular AI accelerator card design in recent years. The difficult design and simulation help domestic and foreign AI companies quickly launch their products

Dense multi-channel LPDDR5 computing card with a maximum operating speed of 6400Mbps

Simulation content

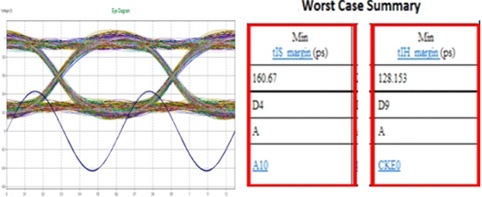

Signal quality simulation:

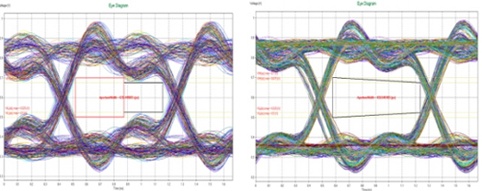

Comparison of results before and after simulation optimization

Signal timing simulation::

-Correspondence of time sequence relationship of each group of signals

-Timing window calculation (build/hold time Margin)